#### Gate Voltaic Transients

## Gate Voltaic Transients

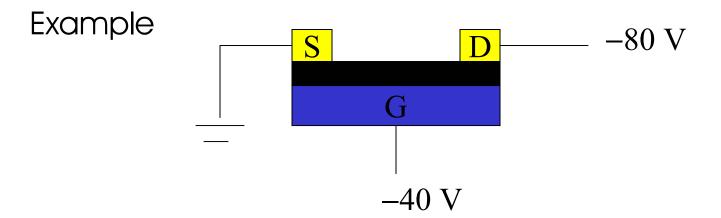

- Not displacement

- Q = Integrated I is too large (Q = DVA  $C_{ox}$ ,  $C_{ox}$  =  $\epsilon_0 \epsilon_r / d_{ox} Q$  = 6.91x10<sup>-7</sup> C)

- $\bullet$  When switching off the voltage, Q doesn't come out.

- For positive  $V_G$ : not same (magnitude of) current.

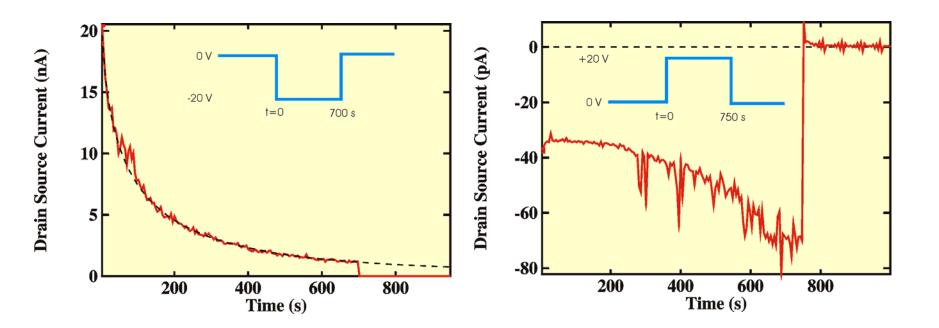

- Follows exponent of square-root-of-time behavior:  $I_{ds} = I_0 \exp(-(t/t)^{0.5}) + I_{off}$

## The Model

# The Model

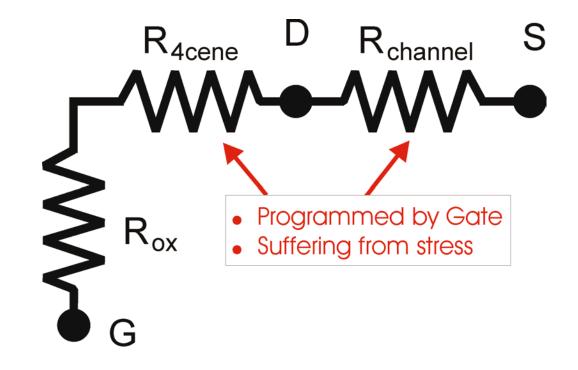

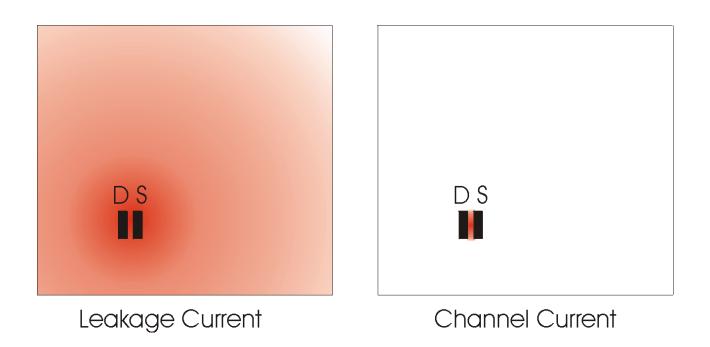

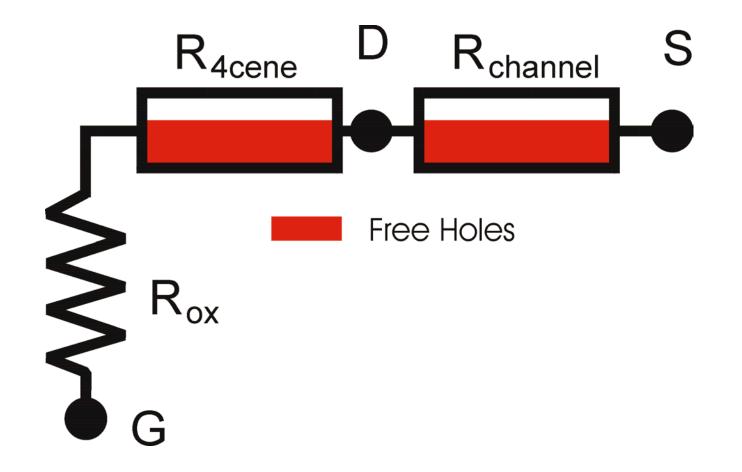

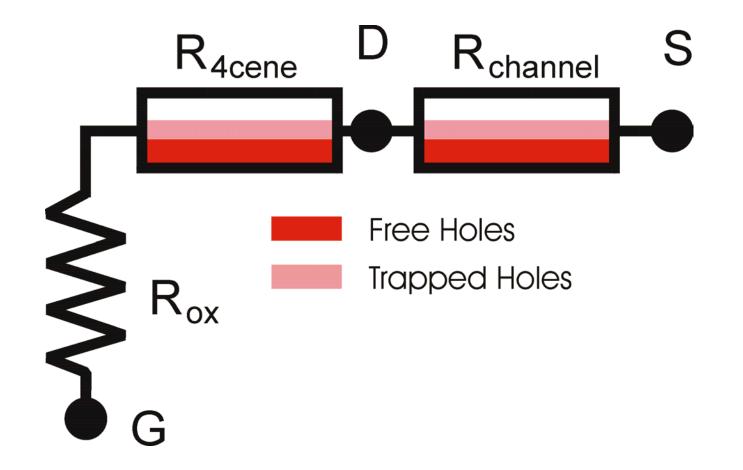

Leakage current and channel current about the same magnitude

Both suffer from trapping of free carriers which increases the resistivity.

### The Model: Transient Behavior

## The Model: Transient Behavior

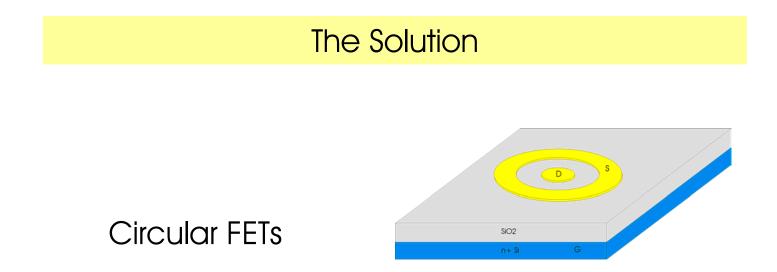

Poor man's alternatives:

Scratching/isolating single devices Also connect pads on side of device to source Measuring always with Vg = Vd

Note: there is no use in masking the edges!

### Ideas / Comments

To set up the **ultra-fast pulse** experiment (Lecroy-Agilent): IEEE cables (2) and interface card (1) are needed urgently.

To study the interfaces of FETs, **sandwich structures** are needed

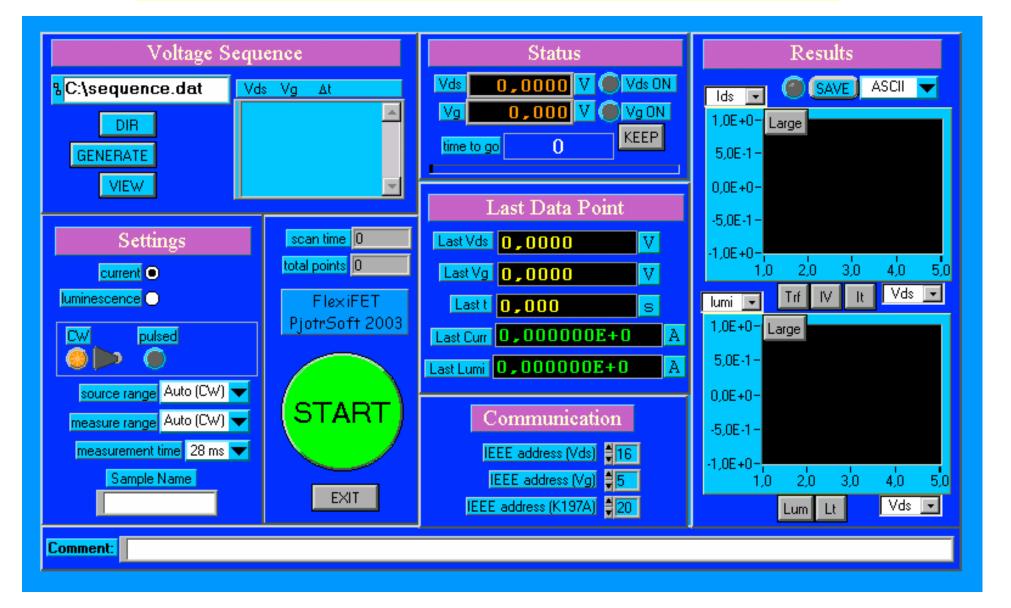

## The FlexiFET program

### Use half-locus curves

Vg = (Vd+Vs)/2

In this way, the drain-source voltage can be increased, without ultrapassing the oxide breakdown voltage anywhere.